- 您现在的位置:买卖IC网 > Sheet目录1996 > HMC700LP4E (Hittite Microwave Corporation)IC FRACT-N PLL 16BIT 24QFN

For price, delivery and to place orders: Hittite Microwave Corporation, 2 Elizabeth Drive, Chelmsford, MA 01824

978-250-3343 tel 978-250-3373 fax Order On-line at www.hittite.com

Application Support: apps@hittite.com

P

LL

-

F

r

a

c

t

io

n

a

L-

n

-

S

M

t

0

0 - 23

HMC700LP4 / 700LP4E

v11.0411

8 GHz 16-Bit Fractional-N PLL

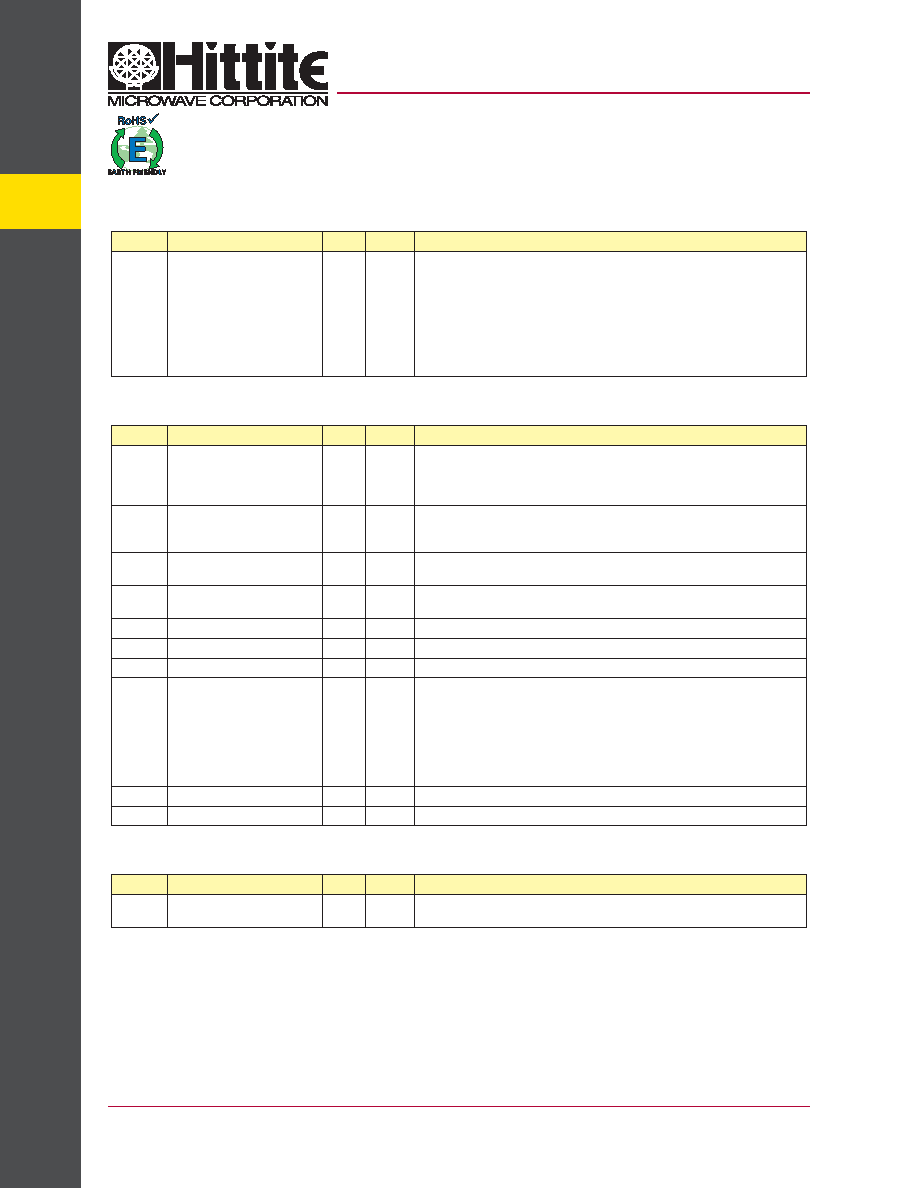

Table 17. Reg 0Ah CP Op Amp Register

Bit

name

Width

Default

Description

[1:0]

cp_opamp_bias_sel

2

0

charge Pump internal op-amp bias select

00 - 540 a

01 - 689 a

10 - 943 a

11 - 1503 a

Enabled with chg Pump enable

note: this circuit affects internal charge pump operation and linearity. Default

setting is recommended. Enabled with reg08h[1] cp_en

Table 18. Reg 0Bh PFD Register

Bit

name

Width

Default

Description

[2:0]

pfd_del_sel

3

0

sets PFD reset path delay. recommended value 010

When in integer mode, reg B Bits [2:0] should not be 000 because it doesn’t

ensure sufficient ‘on’ time for the cP at 50MHz. this isn’t an issue in Fractional

Mode;

[3]

pfd_phase_sel

1

0

Swaps the PFD inputs

1 negative Vco tuning slope

0 positive Vco tuning slope

[4]

pfd_up_en

1

enables the PFD UP output according to state of

pfd_mute_when_locked_enable, see Reg0B<9>

[5]

pfd_dn_en

1

enables the PFD Dn output according to state of

pfd_mute_when_locked_enable, see Reg0B<9>

[6]

pfd_LD_opEn

1

pfd Lock Detect output Enable, enables Lock Detect flag output to LD_SDo pin

[7]

pfd_pullup_ctrl

1

0

Forces PFD UP output on

[8]

pfd_puldn_ctrl

1

0

Forces PFD Dn output on

[9]

pfd_mute_when_locked_

enable

1

0

1: if set:

when locked disables UP if pfd_up_en=0

when locked disables Dn if pfd_dn_en=0

when not locked, allows both UP and Dn to be active and ignores pdf_up_en

and pfd_dn_en

0: if clear, pfd_dn_en and pfd_up_en enable UP and Dn

outputs at all times

[10]

spare0

1

0

reserved

[11]

spare1

1

reserved

Table 19. Reg 0Ch VCO SPI Register

Bit

name

Width

Default

Description

[9:0]

vcospi_vco_data

10

0

data register contents, when written automatically outputs

this data via Vco SPi when to_gpo_sdo=1 Reg09<7>

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HMC703LP4E

IC FRACT-N PLL W/SWEEPR 24QFN

HMC704LP4E

IC FRACT-N PLL 16BIT 24QFN

HMC830LP6GE

IC FRACT-N PLL W/VCO 40QFN

HMP8117CNZ

IC VIDEO DECODER NTSC/PAL 80PQFP

HMP8156ACNZ

IC VIDEO ENCODER NTSC/PAL 64MQFP

HSP45102SC-40Z

IC OSC NCO 40MHZ 28-SOIC

HSP45106JC-33Z

IC OSC NCO 33MHZ 84-PLCC

HSP45116AVC-52Z

IC OSC NCO 52MHZ 160-MQFP

相关代理商/技术参数

HMC700LP4ETR

制造商:Hittite Microwave Corp 功能描述:IC FRACT-N PLL 16BIT 24QFN 制造商:Hittite Microwave Corp 功能描述:HMC700 Series 8 GHz 16-Bit Prescaler Fractional-N PLL - 4x4 mm QFN-24

HMC701LP6C

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:8 GHz 16-BIT FRACTIONAL-N SYNTHESIZER

HMC701LP6C_10

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:8 GHz 16-BIT FRACTIONAL-N SYNTHESIZER

HMC701LP6CE

制造商:Hittite Microwave Corp 功能描述:IC SYNTHESIZER W/SWEEPER 40-QFN

HMC702LP6CE

制造商:Hittite Microwave Corp 功能描述:IC SYNTHESIZER W/SWEEPER 40-QFN

HMC702LP6CE_10

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:14 GHz 16-BIT FRACTIONAL-N SYNTHESIZER

HMC702LP6CE_11

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:14 GHz 16-BIT FRACTIONAL-N PLL

HMC703LP4E

功能描述:IC FRACT-N PLL W/SWEEPR 24QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR